Among of the first announcements coming out of Arm’s TechCon convention in San Jose, is the unveiling of Arm’s new infrastructure branding and a sneak peek at the product roadmap for the next 3 years.

Up till today, the Arm’s IP portfolio for the infrastructure market didn’t differentiate itself much from the regular consumer IP. Today this now changes, as Arm tries to convey its dedicated focus in this market. The new IP portfolio which will see broader announcements over the coming months and years, is now dubbed “Arm Neoverse”.

The Neoverse branding is supposed to be live alongside the usual consumer device oriented Cortex IP branding, meaning that at some point we’ll see a new Neoverse CPU announced whose use-cases are meant to be in the infrastructure space.

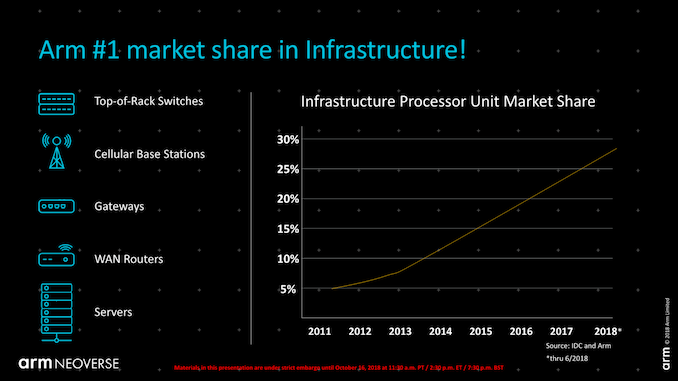

Arm showcases that over the last several years, they’ve been able to capture a significant amount of market share in infrastructure devices. What infrastructure devices actually means, is any kind of non-end user device, such as networking equipment, going from switches, base stations, gateways, router, and most importantly also servers. Here the various Arm vendors have reportedly gained up to a 28% market share.

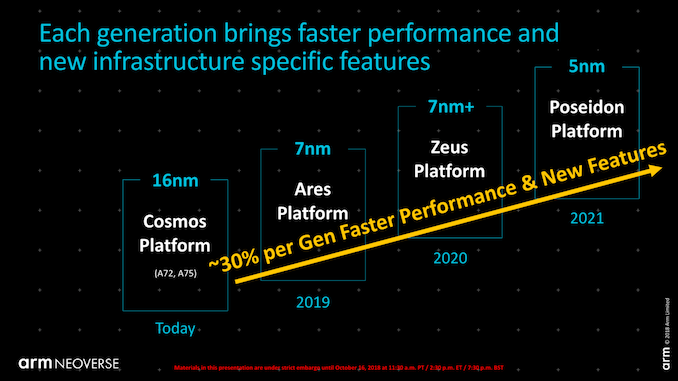

The biggest surprise today was that Arm again has publicly published the roadmap for the next several years, revealing the codenames of the infrastructure focused CPU and platform IPs. As such, we finally see the Ares, Zeus, and Poseidon codenames acknowledged. The CPU IPs based on these codenames should be the sever-oriented counterparts to Enyo/A76, Deimos and Hercules, the latter of which would remain under the Cortex branding. What the differences between the Cortex and Neoverse cores are is still unclear, but among the many possibilities, it’s not hard to imagine that we’ll be seeing SVE implemented in the server IP first.

Arm is also seemingly pushing the performance projections, and promises a 30% jump in performance for each generation over the coming years. This figure is more aggressive than the 20 to 25% quoted CAGR for the Cortex based CPUs in consumer devices, so we’ll likely see more differentiation in the infrastructure IPs.

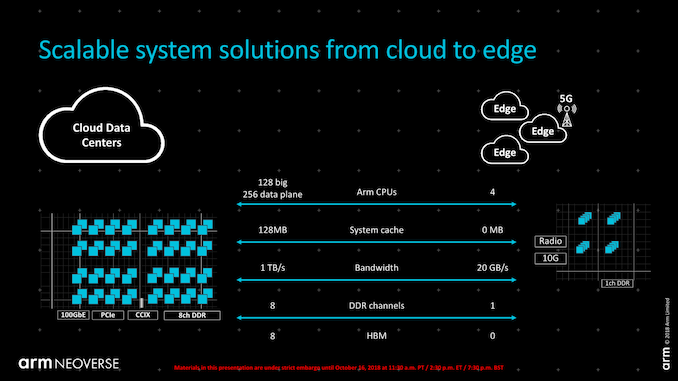

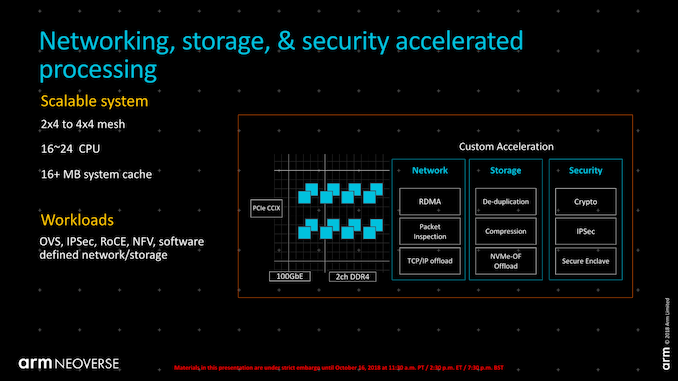

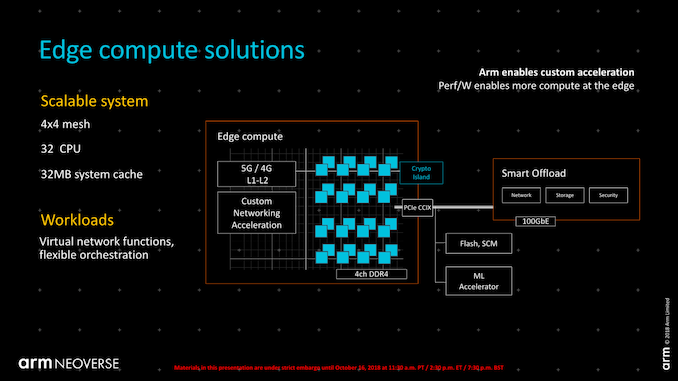

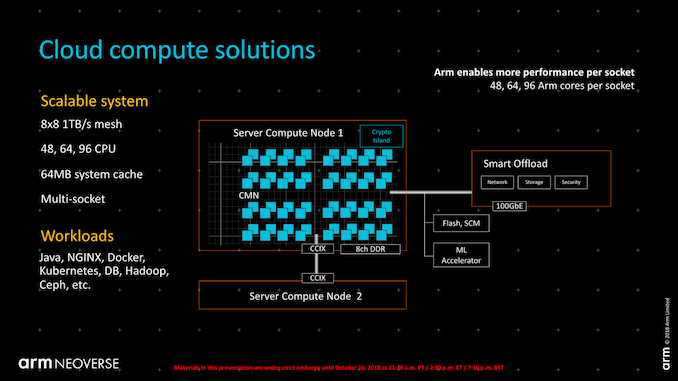

Arm went on to discuss more the various scaling possibilities that vendors can achieve by using Arm’s IP, varying from more simple configurations in edge devices up to very wide implementations for server CPUs, advertising the possibility of 48, 64 or 96 cores per socket in the maximum configuration.

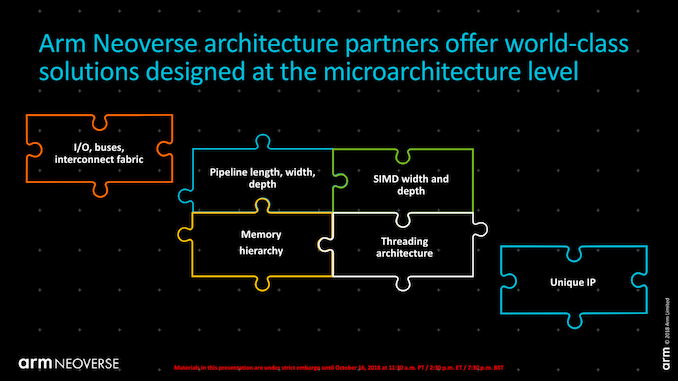

The one slide that really caught my eye and Arm notoriously went over quick was in regards to the offering for architecture partners. Here Arm wants to again communicate that it’s able to provide customised IP on demand, and alter things such as the interfaces to the cores, their memory hierarchy as well as the SVE units’ width and depth. Among these items is also “threading architecture”. While I’m not keen on guessing Arm’s intents here, I do wonder if this means we’ll be seeing SMT implemented in Arm’s Neoverse IPs?

While today’s announcement didn’t have any major technical unveiling, it does put to rest the question how Arm is going to name its new server cores, as well as publicly acknowledging roadmap names and goals for the coming years. Arm promised more details and announcements at TechCon – and we’ll be sure to report on the happenings in the comings days.

from AnandTech https://ift.tt/2RRjjff

via IFTTT